### Performance engineering as a guiding principle for efficient implementations of algorithms in computational science

Habilitationsschrift

zur

Erlangung des akademischen Grades

doctor rerum naturalium habilitatus (Dr. rer. nat. habil.)

an der Mathematisch-Naturwissenschaftlichen Fakultät

der

Ernst-Moritz-Arndt-Universität Greifswald

vorgelegt von Georg Hager geboren am 21.08.1970 in Hof/Saale

Greifswald, im Oktober 2013

| Dekan:                |  |

|-----------------------|--|

| 1. Gutachter:         |  |

| 2. Gutachter:         |  |

| 3. Gutachter:         |  |

| Tag der Habilitation: |  |

### Zusammenfassung

Rechnergestützte Wissenschaften sind zusehends auf paralleles Rechnen angewiesen, um anspruchsvolle numerische Probleme lösen zu können. Die ständig steigende Leistungsfähigkeit paralleler Rechner ermöglicht es zusammen mit Fortschritten in der Algorithmik Modelle zu nutzen, die eine quantitative Beschreibung der Natur erlauben. Dennoch ist auch im Zeitalter der Petaflop-Systeme der Bedarf nach Rechenzyklen immer größer als das Angebot, und Wissenschaftler sind gezwungen, die knappen Ressourcen bestmöglich zu nutzen. Deshalb ist die Effizienz des parallelen Rechnens von entscheidender Bedeutung. Leider wird Effizienz leicht mit Skalierbarkeit verwechselt, was dann zu Problemen führt, wenn parallele Programme nur deswegen skalieren, weil die Ausführung des Codes in den Recheneinheiten so langsam ist.

Performance-Modellierung und Performance-Engineering auf der Ebene der Rechenknoten sind die Hauptthemen dieser Arbeit. Performance Engineering wird als Prozess verstanden, der ein tieferes Verständnis der Wechselwirkung von Hardware mit Software ermöglicht. Dies führt zu einem wohldefinierten Konzept von "bestmöglicher Performance". Zu diesem Zweck verwendet Performance-Engineering ressourcengetriebene Performancemodelle, um die Laufzeit des Codes und den Nutzen von Optimierungen vorherzusagen. Ein Performancemodell basiert auf einem vereinfachten Maschinenmodell, das die wichtigsten Elemente einer Rechnerarchitektur umfasst.

Diese Arbeit beginnt mit einem Überblick über die Architektur moderner multicore-Prozessoren und Rechenknoten, soweit sie relevant für die ressourcengetriebene Performancemodellierung ist. Nach einer Einführung in das bekannte Roofline-Modell wird das "Execution-Cache-Memory-Modell" (ECM-Modell) präsentiert, das als Verfeinerung des Roofline-Modells für multicore-CPUs gesehen werden kann. Das ECM-Modell ist insbesondere fähig, die Einzelkern-Performance und die Skalierung von Schleifenkonstrukten mit kontinuierlichem Speicherzugriff über die Rechenkerne eines Chips vorherzusagen.

Da die Leistungsaufnahme von Großrechnern und damit der Energieverbrauch der darauf genutzten Codes wegen der steigenden Kosten für die Infrastruktur immer mehr in den Fokus rückt, werden die Eigenschaften paralleler Programme im Hinblick auf diese Faktoren in naher Zukunft von zentraler Bedeutung sein. Die Frage, mit welchen Mitteln Energie gespart werden kann, ohne die Performance zu kompromittieren, kann mit Hilfe von *Energiemodellen* geklärt werden. Dazu wird ein phänomenologisches Energiemodell für multicore-Chips eingeführt, das den optimalen Arbeitspunkt in Bezug auf die Anzahl genutzter Kerne und die Taktfrequenz vorhersagen kann. Als wichtigste Einflussgröße geht dabei jedoch die Performance des Codes ein. Folglich bekommt das "race to idle"-Konzept im Rahmen des Energiemodells eine Doppelbedeutung: Energie kann sowohl durch effizienten Code als auch durch hohe Taktfrequenz gespart werden. Ersteres funktioniert immer, letzteres nur in einem bestimmten, durch statische und dynamische Leistungsaufnahme definierten Bereich.

Performance- und Energiemodelle können bei der Entwicklung effizienter Software behilflich sein, sie sollten jedoch in einen wohlstrukturierten Prozess eingebettet werden, der die Komplexität der Hardware-Software-Wechselwirkung handhabbar macht. *Mustergeleitetes Performance-Engineering* ist solch ein Prozess. Dazu wird eine Anzahl vorherrschender Performancemuster auf Knotenebene identifiziert und auf Signaturen abgebildet, die jeweils aus einem beobachtbaren Performanceverhalten und einer Kombination von Hardware-Metriken besteht. Diese Muster werden dann zur Konstruktion von Performancemodellen eingesetzt, die durch Messungen bestätigt oder widerlegt werden. Da es sich um einen iterativen Prozess handelt, führt ein widerlegtes Modell zu neuen Einsichten, wenn ein neues Muster ausgewählt und/oder ein neues Modell konstruiert wird. Andererseits hat ein erfolgreiches Modell das Potenzial zur Vorhersage des möglichen Nutzens von Programmoptimierungen. Dadurch wird die Methode "Versuch und Irrtum" durch ein wohlbegründetes Vorgehen ersetzt.

### Abstract

Computational science relies heavily on parallel computing to solve challenging numerical problems. The ever-increasing performance of parallel computers together with algorithmic advances enables high-performance software to use models that provide quantitative descriptions of natural phenomena. However, the demand for compute cycles is always larger than the supply even in the petascale era, so scientists are hard-pressed to make best use of the scarce resources. This is why the *efficiency* of parallel computing is paramount. Unfortunately, efficiency is often confused with *scalability*, which is problematic since it is easy to make a parallel program scale by slowing down its code execution in the processors and compute nodes doing the actual work.

Performance modeling and performance engineering approaches on the node level are the main topics of this work. *Performance engineering* is understood as a process that helps in developing a thorough understanding of the interactions between software and hardware, leading to a well-defined concept of "best performance." To this end, performance engineering builds on *resource-driven performance models* to predict the runtime of code and the benefit of optimizations. Performance models are based on simplified machine models, which encompass the key features of a computer architecture.

This treatise starts with giving an overview on processor and node architecture, as far as it is relevant for resource-driven performance modeling. After an introduction to the well-known roofline model, the execution-cache-memory (ECM) performance model is presented as a refinement of the roofline model that is especially useful in predicting the single-core performance and multicore scalability of streaming loop kernels.

Since the power dissipation of computer systems, and hence the energy consumption of running programs, is gaining attention due to growing costs for the infrastructure of large installations, energy-awareness will be a cardinal quality of computer code in the near future. How to save energy with minimum loss of performance is the key question, which may be answered by power modeling techniques. For this purpose a phenomenological multicore power model is introduced. It can predict optimal operating points with respect to chip-level concurrency and processor clock speed for parallel code, but one of the main premises that go into the model is that code performance is the lowest-order energy-saving factor. Consequently, the *race to idle* concept has a double meaning in the model: Racing by code efficiency and racing by clock speed. While the former is always applicable, the latter only saves energy in a certain parameter range of static vs. dynamic power.

Using performance (and power) modeling is a way to learn more about efficient code execution, but such models should be embedded in a well-structured process that guides the way through the complexities of hardware-software interactions. *Pattern-driven structured performance engineering* provides such a process. A number of prevalent node-level performance patterns is defined, together with identifying signatures in performance behavior and hardware metrics. These patterns are then used to construct models, which can be validated or falsified using measurements. Since the process is iterative, a false model has the positive effect that new insights are gained as a new model is built or a new pattern is selected. A working model, on the other hand, has the potential to predict the possible gain of code optimizations, and substitutes trial-and-error by well-founded decisions.

### Clarification about use of prior own work

This treatise contains new results as well as results that were previously published by the author and his co-authors. In cases where larger portions of previous work were used literally or almost literally, the section header has a reference to this prior own work. This pertains especially to the following sections and publications:

- Sect. 2.4.1 [1]

- Sect. 3.3.2 [2, 3]

- Sect. 3.4 [4, 1]

- Chapter 4 [1]

- Sect. 5.2 [5]

- Chapter 6 [6]

- Chapter 7 [7]

## Contents

| Li | List of acronyms and abbreviations |          |                                                                     | 5    |

|----|------------------------------------|----------|---------------------------------------------------------------------|------|

| Ι  | Per                                | forman   | nce modeling and engineering                                        | 7    |

| 1  | Intro                              | oductio  | n                                                                   | 9    |

|    | 1.1                                | Scienti  | ific computing and code optimization                                | . 9  |

|    | 1.2                                | Perform  | mance modeling                                                      | . 9  |

|    |                                    | 1.2.1    | Light speed                                                         | . 10 |

|    |                                    | 1.2.2    | Extrapolation                                                       | . 10 |

|    |                                    | 1.2.3    | Machine model                                                       | . 11 |

|    | 1.3                                | Contri   | butions                                                             | . 11 |

|    |                                    | 1.3.1    | ECM Model                                                           | . 11 |

|    |                                    | 1.3.2    | Multicore power model                                               | . 11 |

|    |                                    | 1.3.3    | Pattern-guided structured performance engineering on the node level | . 12 |

|    |                                    | 1.3.4    | Applications                                                        | . 12 |

|    | 1.4                                | Relate   | d work in performance engineering                                   | . 14 |

|    | 1.5                                | Organi   | ization of this thesis                                              | . 15 |

| 2  | Con                                | nputer a | architecture                                                        | 17   |

|    | 2.1                                | Cores    |                                                                     | . 17 |

|    |                                    | 2.1.1    | Execution units and ports                                           | . 17 |

|    |                                    | 2.1.2    | Registers                                                           | . 19 |

|    |                                    | 2.1.3    | SIMD execution                                                      | . 19 |

|    |                                    | 2.1.4    | Instruction cache and decoders                                      | . 20 |

|    |                                    | 2.1.5    | SMT                                                                 | . 20 |

|    |                                    | 2.1.6    | Data cache                                                          | . 21 |

|    |                                    | 2.1.7    | Clock frequency and turbo mode                                      | . 21 |

|    | 2.2                                | Multic   | core chips                                                          | . 21 |

|    |                                    | 2.2.1    | Multiple cores                                                      | . 21 |

|    |                                    | 2.2.2    | Memory access                                                       | . 22 |

|    | 2.3                                | Node a   | and memory architecture                                             | . 22 |

|    | 2.4                                | Test be  | ed and tools                                                        | . 23 |

|    |                                    | 2.4.1    | Intel Xeon "Sandy Bridge" processor                                 | . 23 |

|    |                                    | 2.4.2    | Tools                                                               | . 24 |

|    |                                    | 2.4.3    | SuperMUC                                                            | . 24 |

| 3 | Whi  | te-box j | performance modeling on the chip level                             | 27 |

|---|------|----------|--------------------------------------------------------------------|----|

|   | 3.1  | Perform  | mance and speedup                                                  | 27 |

|   |      | 3.1.1    | Useful performance metrics                                         | 28 |

|   |      | 3.1.2    | High-level scalability models                                      | 28 |

|   | 3.2  | The ro   | ofline model                                                       | 30 |

|   |      | 3.2.1    | Building the model                                                 | 30 |

|   |      | 3.2.2    | Model prerequisites and assumptions                                | 31 |

|   |      | 3.2.3    | Model-guided code optimizations                                    | 32 |

|   | 3.3  | Examp    | ples for roofline modeling                                         | 34 |

|   |      | 3.3.1    | Pure streaming kernel                                              | 34 |

|   |      | 3.3.2    | Sparse matrix-vector multiplication                                | 36 |

|   |      | 3.3.3    | Divide-accumulate kernel                                           | 41 |

|   |      | 3.3.4    | Conclusions and best practices for applying the roofline model     | 42 |

|   | 3.4  | The Ex   | xecution-Cache-Memory (ECM) model: A refined performance model for |    |

|   |      | stream   | ing loop kernels on multicore                                      | 43 |

|   |      | 3.4.1    | The Execution-Cache-Memory (ECM) model: Single core                | 43 |

|   |      | 3.4.2    | The ECM model: Multicore scaling                                   | 45 |

|   |      | 3.4.3    | Validation via streaming benchmarks                                | 46 |

|   |      | 3.4.4    | Conclusions and best practices for applying the ECM model          | 50 |

|   | 3.5  | Chapte   | er summary                                                         | 51 |

| 4 | Perf | ormanc   | ce and power                                                       | 53 |

|   | 4.1  | Power    | dissipation and performance on multicore                           | 53 |

|   |      | 4.1.1    | Power and performance of benchmarks vs. active cores               | 53 |

|   |      | 4.1.2    | Power and performance vs. clock frequency for all benchmarks       | 56 |

|   |      | 4.1.3    | Conclusions from the benchmark data                                | 58 |

|   | 4.2  | A qual   | litative power model                                               | 58 |

|   |      | 4.2.1    | Minimum energy with respect to the number of active cores          | 60 |

|   |      | 4.2.2    | Minimum energy with respect to code performance                    | 60 |

|   |      | 4.2.3    | Minimum energy with respect to clock frequency                     | 61 |

|   |      | 4.2.4    | Validation of the power model for the benchmarks                   | 62 |

|   | 4.3  | Conse    | quences for system design                                          | 63 |

|   | 4.4  | Chapte   | er summary                                                         | 65 |

| 5 | Stru | ctured   | performance engineering                                            | 67 |

|   | 5.1  | The pe   | erformance engineering process                                     | 67 |

|   |      | 5.1.1    | Description of the process                                         | 67 |

|   |      | 5.1.2    | Case study: An OpenMP-parallel 3D Jacobi smoother                  | 70 |

|   | 5.2  | Identif  | fication of performance patterns on the node level                 | 78 |

|   |      | 5.2.1    | Hardware performance metrics                                       | 78 |

|   |      | 5.2.2    | likwid-perfctr                                                     | 79 |

|   |      | 5.2.3    | Performance patterns and event signatures                          | 79 |

|   |      | 5.2.4    | Pattern categorization                                             | 85 |

|   | 5.3  | Patterr  | ns and models: Performance engineering refined                     | 85 |

### **II** Applications

| 0 | • |

|---|---|

| x | u |

| Ο | " |

| 6 | A m | edical image reconstruction algorithm                           | 91  |

|---|-----|-----------------------------------------------------------------|-----|

|   | 6.1 | Introduction                                                    | 91  |

|   |     | 6.1.1 Computed tomography                                       | 91  |

|   | 6.2 | Experimental testbed                                            | 93  |

|   | 6.3 | The algorithm                                                   | 93  |

|   |     | 6.3.1 Theory                                                    | 93  |

|   |     | 6.3.2 Code analysis                                             | 94  |

|   |     | 6.3.3 Simple performance models                                 | 96  |

|   |     | 6.3.4 Algorithmic optimizations                                 | 97  |

|   | 6.4 | Single core optimizations                                       | 98  |

|   |     | 6.4.1 SIMD vectorization                                        | 98  |

|   |     | 6.4.2 AVX implementation                                        | 100 |

|   | 6.5 | In-depth performance analysis                                   | 101 |

|   |     | 6.5.1 ECM performance model                                     | 101 |

|   |     | 6.5.2 ILP optimization and SMT                                  | 103 |

|   | 6.6 | OpenMP parallelization                                          | 103 |

|   |     | 6.6.1 ccNUMA placement                                          | 104 |

|   |     | 6.6.2 Blocking/unrolling                                        | 104 |

|   | 6.7 | Results                                                         | 105 |

|   |     | 6.7.1 Validation of analytical predictions                      | 105 |

|   |     | 6.7.2 Parallel results                                          | 105 |

|   | 6.8 | Conclusion                                                      | 106 |

|   |     | 6.8.1 Summary of results                                        | 106 |

|   |     | 6.8.2 Reassessment in view of performance patterns              | 107 |

| 7 | A p | erformance- and energy-optimized lattice-Boltzmann fluid solver | 109 |

|   | 7.1 | Introduction                                                    | 109 |

|   |     | 7.1.1 Related work                                              | 109 |

|   |     | 7.1.2 The lattice-Boltzmann method                              | 110 |

|   |     | 7.1.3 Implementation options and data traffic analysis for LBM  | 111 |

|   |     | 7.1.4 Test bed and benchmark cases                              | 113 |

|   | 7.2 | Chip-level performance and scaling                              | 113 |

|   | 7.3 | ECM model for the ILBDC code                                    | 115 |

|   |     | 7.3.1 In-core analysis                                          | 115 |

|   |     | 7.3.2 Data transfers and saturation behavior on the chip        | 115 |

|   |     | 7.3.3 Validation of the performance model                       | 118 |

|   | 7.4 | Power model                                                     | 118 |

|   |     | 7.4.1 Energy to solution for the LBM solver on the chip         | 119 |

|   | 7.5 | Highly parallel LBM simulations                                 | 121 |

|   |     | 7.5.1 MPI parallelization in ILBDC                              | 121 |

|   |     | 7.5.2 Performance and energy at strong scaling                  | 122 |

|   | 7.6 | Conclusion                                                      | 126 |

|   |     | 7.6.1 Summary of results                                        | 126 |

|   |     | 7.6.2 Reassessment in view of performance patterns              | 127 |

| 8   | Conclusion |         |     |  |  |  |  |

|-----|------------|---------|-----|--|--|--|--|

|     | 8.1        | Summary | 29  |  |  |  |  |

|     | 8.2        | Dutlook | 31  |  |  |  |  |

| Bil | bliogr     | phy 1   | .33 |  |  |  |  |

# List of acronyms and abbreviations

| AoS    | Array of structures                                      |

|--------|----------------------------------------------------------|

| AVX    | Advanced vector extensions                               |

| BP     | Backprojection                                           |

| ccNUMA | Cache-coherent nonuniform memory access                  |

| CFD    | Computational fluid dynamics                             |

| CISC   | Complex instruction set computer                         |

| CL     | Cache line                                               |

| CPI    | Cycles per instruction                                   |

| CPU    | Central processing unit                                  |

| CRS    | Compressed row storage                                   |

| CT     | Computed tomography                                      |

| DCT    | Dynamic concurrency throttling                           |

| DDR    | Double data rate                                         |

| DP     | Double precision                                         |

| DRAM   | Dynamic random access memory                             |

| ECM    | Execution-cache-memory                                   |

| Flop   | Floating-point operation                                 |

| FLUP   | Fluid lattice site update                                |

| FMA    | Fused multiply-add                                       |

| FP     | Floating point                                           |

| FPGA   | Field-programmable gate array                            |

| GPGPU  | General-purpose (computing on) graphics processing units |

| HPC    | High performance computing                               |

| HPM    | Hardware performance monitoring                          |

| HT     | HyperTransport                                           |

| IACA   | Intel architecture code analyzer                         |

| IB     | InfiniBand                                               |

| ILP    | Instruction-level parallelism                            |

| IMB    | Intel MPI benchmarks                                     |

| I/O    | Input/output                                             |

|        |                                                          |

| L1D    | Level 1 data cache                  |

|--------|-------------------------------------|

| L1I    | Level 1 instruction cache           |

| L2     | Level 2 cache                       |

| L3     | Level 3 cache                       |

| LD     | Locality domain                     |

| LIKWID | Like I knew what I'm doing          |

| LUP    | Lattice site update                 |

| MPI    | Message passing interface           |

| MVM    | Matrix–vector multiplication        |

| NT     | non-temporal                        |

| OLC    | Outer-level cache                   |

| OS     | Operating system                    |

| PCI    | Peripheral component interconnect   |

| PDF    | Particle distribution function      |

| QDR    | Quad data rate                      |

| QPI    | QuickPath interconnect              |

| RAM    | Random access memory                |

| RAPL   | Running average power limit         |

| RCM    | Reverse Cuthill-McKee               |

| RISC   | Reduced instruction set computer    |

| RHS    | Right hand side                     |

| RFO    | Read for ownership                  |

| SIMD   | Single instruction multiple data    |

| SMP    | Symmetric multiprocessing           |

| SMT    | Simultaneous multithreading         |

| SoA    | Structure of arrays                 |

| SP     | Single precision                    |

| spMVM  | Sparse matrix-vector multiplication |

| SSE    | Streaming SIMD extensions           |

| TDP    | Thermal design power                |

| TLB    | Translation lookaside buffer        |

| TRT    | Two relaxation-time                 |

### Part I

# **Performance modeling and engineering**

### Chapter 1

### Introduction

### **1.1** Scientific computing and code optimization

Computing has become the third pillar of scientific research besides theory and experiment. It is today an indispensable tool, and deeply interwoven with most areas of science and engineering. In many cases the required computing power is quite small and can be handled by a user's own laptop; other applications need vast computational resources such as federal computing centers in order to gain even qualitative results. Then it is necessary to think about how these systems can be used most effectively, so that the money spent in their procurement and operation has the highest possible impact.

Unfortunately, the domain scientists who write the software for parallel computers do not have the required knowledge to write efficient code. Even if an appropriate algorithm has been chosen, implementations often lack the ability to make best use of the resources. As a first step to remedy this unsatisfactory situation, computing centers offer compact courses and lectures, trying to teach at least the basic aspects of computer architecture, code parallelization, and optimization. As a consequence, many domain scientists spend more time on their code in an effort to make it "faster," applying the strategies learned. While this is a commendable endeavor, there is always the question when to stop optimizing, i.e., when the performance of the application code is "good enough." If the best possible performance level is unknown, the invested time and resources may far outweigh the benefit. This typical pattern is related to a disregard for the "80/20 rule," also called the "Pareto principle" [8]: Eighty percent of the effects are due to twenty percent of the causes. Translated to high-performance software development this means "twenty percent of the effort spent in optimization lead to eighty percent of the possible benefit." But again, an unknown possible benefit makes applying this rule impossible.

### **1.2** Performance modeling

Performance modeling in a broad sense means establishing a mathematical model for software/hardware interaction in order to predict or explain the runtime characteristics of a program on a given hardware. More specifically, performance modeling can have two different but sometimes overlapping goals: light speed calculation or extrapolation.

### 1.2.1 Light speed

A realistic upper limit for the performance of a code on a particular hardware may be called its *light speed*. Light speed allows a well-defined answer to the question whether an implementation of an algorithm is "good enough." A model leading to an accurate light speed estimate requires thorough code analysis, knowledge of computer architecture, and experience on how software interacts with hardware. The notion of light speed depends very much on the machine model underlying the hardware model; if the machine model misses an important performance-limiting detail, one might arrive at the (false) conclusion that light speed is not attained by the code at hand, while it actually is. Which hardware features should be included to arrive at a good balance between simplicity and predictive power is a crucial question, to which this work tries to give useful answers.

We call this approach *white-box performance modeling*. In complex cases it may not be possible to establish a model at all. If a model can be built, one can gain a deeper understanding of the interactions between software and hardware. If the model works, this is an indication that it describes certain aspects of this interaction accurately. If the model does not work (e.g., if the predicted performance is much lower or higher than the measured performance), it must be refined, leading to more insights.

A working model can help with predicting the possible gain of code optimizations. Changing the program code may require adjustments in the model, or even building a completely new model when the underlying algorithm was changed.

### **1.2.2** Extrapolation

Another goal of performance modeling is to extrapolate performance behavior from one hardware (e.g., a small system, or a given architecture) to different hardware (e.g., a large system, or a different architecture), which may not even exist yet, and for which only the specifications might be known. The assessment of performance characteristics on the known hardware can take a variety of forms. One option is to build on the first goal above, and then change the model parameters to accommodate the change to the new hardware. Alternatively one may take the code on the known hardware "as is" and try to figure out which hardware characteristics have the most impact on its performance. We call this *black-box performance modeling*, because the focus is not on understanding underlying mechanisms but on producing an accurate mathematical description, with accuracy defined only in terms of predictive power and not in terms of precision in describing the true underlying mechanisms. Less insight into the hardware-software interaction is gained by this approach, but there is the big advantage that it can often be used in very complex scenarios, where the other strategies fail. The statistical nature of the models thus obtained sometimes lead to the discovery of effects that would otherwise go unnoticed. See Sect. 1.4 on related work below for an example.

Fortunately the "80/20 rule" also applies to the performance characteristics of many programs in computational science: Most of the runtime is spent in a small part of the code. Consequently, the performance profile of many applications, i.e., the distribution of time over functions or loops, tends to be simple, and light speed techniques are applicable.

### 1.2.3 Machine model

As mentioned above, the interaction of software with hardware can be modeled to various levels of sophistication. Little variation exists in evaluating the requirements of the program code; the worst that could happen is that the assembly code generated by a compiler must be analyzed to uncover problems with inefficient execution.

On the other hand, there is a considerable bandwidth of possible machine models. Parallel computers are complex machines, but they are in principle deterministic. It would thus be possible to use a "cycle-accurate" simulator of the hardware to emulate the code execution and be able to acquire every possible detail. In practice, this approach would be unrewarding. Firstly, cycle-accurate models of real, modern processors exist but are intellectual property that is not divulged by chip manufacturers. Beyond the chip level, the sheer complexity of system components and their interactions rule out cycle-accurate models. Secondly, even if a cycle-accurate model were available it would not be of much use, because it would require considerable expertise, even beyond the level of a professional HPC expert, to interpret the results.

As a compromise one can establish simplified machine models, which are simple enough to be understood completely but which also allow for sufficiently predictive performance modeling. Applied in this sense, performance modeling is similar to the modeling techniques used in the natural sciences: It is implicit that the model is "wrong," i.e., that it does not encompass all possible effects, and that there might be assumptions going into it that are in no way justified. However, it is useful enough to understand the key mechanisms and probably predict new effects that have not been encountered or looked at before. If the model fails, its assumptions and simplifications are challenged, and new insight is gained.

### **1.3 Contributions**

This section summarizes the essential contributions described in this treatise.

### 1.3.1 ECM Model

The "Execution-Cache-Memory" white-box performance model is a refinement of the wellknown roofline model for predicting the performance and scalability of streaming loop kernels on multicore processors. It is to date the only approach that uses a simple machine model to arrive at an accurate single-core performance prediction for a real processor. Compared to the roofline model it drops some crucial assumptions and needs less phenomenological input. The roofline model can be seen as the "saturation limit" of the ECM model.

The ECM model has so far been applied to simple microbenchmark kernels [4, 1], to stencil algorithms of varying complexity [9, 10], to lattice-Boltzmann flow solvers [1, 7], and to a volume reconstruction algorithm from medical image processing [6]. Some of these applications will be revisited here (see below).

### **1.3.2** Multicore power model

Energy consumption aspects of computing have been moving into the focus of research in recent years. The multicore power model is a phenomenological description of the energy consumption of load-balanced parallel code on a multicore processor, taking into account the clock speed, the

number of utilized cores, the single-thread performance, and the maximum (saturated) performance, and the static and dynamic power consumption (per core). When energy consumption is an important metric, it answers questions such as "Is it better to use more cores at lower frequency or fewer cores at higher frequency?", "What is the optimum clock speed for a code that scales/saturates across the cores?", "Which influence does single-thread performance have on energy consumption?", etc. The model can also be used for design space exploration, and allows to estimate the trade-offs between a system's size and its energy consumption over its lifetime.

Combining the power model with the ECM model is especially interesting for saturating (i.e., bandwidth-bound) codes, enabling energy and performance optimization at the same time for an optimal selection of the operation point (number of cores used, clock speed).

#### **1.3.3** Pattern-guided structured performance engineering on the node level

Structured performance engineering can be seen as a part of software engineering. It is an iterative process in which algorithm and code analysis, performance modeling, and optimization are applied repeatedly to arrive at a well-defined concept of "best possible performance." Its goal is to replace "shot-in-the-dark" optimizations, for which the possible outcome is unknown, with code changes whose performance impact was *expected*. This kind of structured approach is vital for the computational scientist, for whom programming is just a means to an end. It still requires some expertise in modeling and computer architecture, however, but the process also provides guidelines to how this knowledge may be best conveyed in courses and lectures.

The simple but instructive example of a 3D Jacobi smoother is used to show the advantages of structured performance engineering. While all optimizations and models applied to this case are well known, the embedding in a performance engineering process is new, and can be extrapolated to more complex cases.

The performance engineering process is supported by *performance patterns*. A pattern is a combination of observed performance behavior and data obtained from hardware performance monitoring. Instead of blindly applying tools to find "problems," the developer uses tools for the specific purpose of validating or refuting a performance model. A collection of relevant patterns for node-level performance engineering is identified and categorized into *maximum resource usage, hazards*, and *work inefficiency*. With the help of patterns, "best performance" gets a well defined meaning as "computing at a bottleneck."

Although the process is generally applicable to all kinds of parallel computing, this work is mostly restricted to the chip and node level, where the actual computational "work" is done.

### 1.3.4 Applications

The ECM model, the power model, and the concepts developed in the structured performance engineering process are applied to several application cases.

#### Sparse matrix-vector multiplication

Many algorithms in computational science require sparse linear algebra: Sparse eigensolvers, numerical methods for time evolution of quantum systems, finite-difference and finite-element

in fluid and structural mechanics, etc. These usually require high-performance sparse matrixvector multiplication (spMVM) as a dominating, or at least significantly time-consuming component. SpMVM is also an example where predictive modeling is problematic, but where the general idea of a performance model can still be used with success. The roofline model is used to assess the quality of parallel spMVM implementations, establish upper performance limits, and lead to a better understanding of how well resources are utilized. Taking into account how much compute resources go into spMVM, a statement about when an implementation is "good enough" can be of great value. Moreover, the performance of spMVM depends heavily on the matrix structure, i.e., the location of the non-zero entries. Performance modeling is able to predict the advantage from matrix reordering techniques.

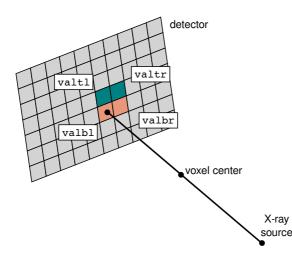

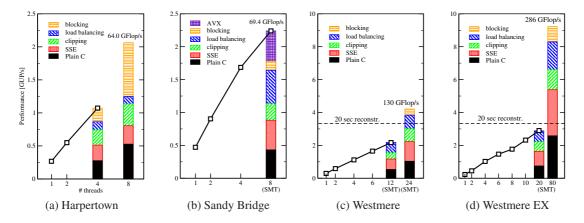

#### A volume reconstruction algorithm in medical physics

Backprojection (BP) algorithms are used in 3D volume reconstruction from images delivered by computed tomography (CT) devices. The performance of an implementation is strictly limited from below due to the use of interventional CT imaging techniques in modern surgery. Performance engineering can be used to understand the key requirements of a BP algorithm implementation to the hardware. This is an especially interesting case since there is usually not a single performance-limiting aspect like peak arithmetic throughput or data transfers. Via through performance modeling one can identify shortcomings of current standard processor architectures and propose improvements that could make a difference in reconstruction performance or enable higher-resolution imaging at constant cost. Especially for the case of multicore processors, the model predicts that it is possible to meet the required performance goal in current clinical CT applications without resorting to special-purpose hardware like GPGPUs or FPGAs. It can also identify a definite cross-over point where one or the other architecture is more advantageous with respect to performance or price/performance.

BP is a complex example where the first attempt at performance modeling via the roofline model fails completely because of unjustified assumptions about code execution on the hard-ware and the applicable performance pattern. Changing the pattern, using the ECM model, and applying guided code optimizations one is able to arrive at a code that fulfills the clinical performance limit (which happens to be a very precise definition of "good enough"). In the end, it is not a single one but a combination of patterns that apply.

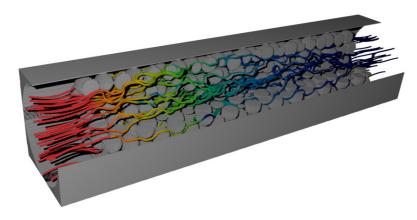

#### Performance and energy optimization of a lattice-Boltzmann algorithm

The lattice Boltzmann method (LBM) is today established as a successful alternative to traditional flow solvers. LBM is traditionally believed to be memory-bound on all modern computer architectures, but the details are complex to fathom. A sparse-lattice implementation of a two-relaxation-time (TRT) LBM algorithm is used to answer the question for "best possible performance" on multicore systems. The influence of SIMD vectorization, the processor clock frequency, and the propagation pattern on the performance and energy consumption of the solver is studied using a combination of the ECM and power models. This enables an understanding of the complex interplay between in-core execution and data transfers, and leads to definite predictions about the performance of an implementation and to the identification of an energy-performance optimization space. Since this implementation is MPI-parallel it is also possible to study if and how the consistent picture obtained on the socket level can be generalized to the highly parallel, distributedmemory case with strong scaling. It turns out that non-negligible MPI communication introduces not only overhead but also a core-bound component into the code execution characteristics, which has decisive influence on the optimal performance/power operating point. Since the energy consumption characteristics of memory-bound and core-bound codes are conflicting in terms of the optimal clock speed, especially when the baseline power dissipation of the whole system is taken into account, the optimization space for performance and power becomes very sharply defined. High single-core performance and an optimal choice of the number of cores used per socket are the dominant factors. In other words, mediocre-quality code running at a low clock speed (because there is an implicit assumption about memory-boundedness) wastes compute cycles and energy at the same time.

### **1.4 Related work in performance engineering**

This section describes related work relevant for the performance modeling and engineering approaches. All other relevant related work, especially for the application cases in Part II, will be covered in the respective sections.

White-box performance modeling has been used for a long time. In the times of single-core in-order scalar processor architectures, where each instruction had a well-defined duration, accurate runtime predictions on the chip level were possible without simplifications. Out-of-order superscalar designs rendered this option impossible. The roofline model reduces machine and code properties to a small number of parameters: computational intensity, memory bandwidth, and peak performance. Although the term has been coined by Williams et al. [11], the model has been in use since the 1980s [12], and was an integral part of performance optimization on vector and early parallel computers [13].

Beyond the node level, a lot of effort has been invested in performance modeling of massively parallel applications [14, 15, 16, 17]. The work of Petrini et al. [15] is especially interesting since it used performance models to identify the previously unknown problem of *operating system noise* as a main factor limiting the scalability of large-scale bulk-synchronous code. It is a supreme case for the notion that valuable insight is gained when a model fails.

In order to manage the complexity of modeling modern systems (also in the highly parallel, distributed case) and to lower the required expertise for users, a number of simulation-based systems have been devised, for example the Warwick Performance Prediction toolkit (WARPP) [18] and its predecessors. They use a combination of compiler-based instrumentation, trace collection, and simulation to arrive at runtime predictions even for highly complex, massively parallel applications. In contrast, the performance engineering process described in this work relies on patterns, thorough manual or tool-based sequential code analysis, and experience, to gain insight into software-hardware interaction.

One of several interesting automatic tools that can help in identifying performance bottlenecks also for inexperienced users is PerfExpert [19]. It provides node-level tuning advice based on application tracing with hardware performance metrics. There is an implicit use of patterns in the tool, and it exposes to the user the possible bottlenecks and their severity on a loop-by-loop (or basic block) basis. Nevertheless, such an analysis can only be a starting point and considerable experience is still required to take the necessary actions for improving code performance. There are very few activities in the field of structured performance engineering that do not build on automatic frameworks. One recent approach was described in [20], where a useful workflow was developed in the specific context of optimizing OpenMP code for modern multicore systems and accelerators.

### **1.5** Organization of this thesis

This work is organized as follows. Chapter 2 gives a high-level overview on core, processor, and node architecture, as far as it is required for the modeling approaches described later. The Intel Xeon Sandy Bridge processor is the dominant architecture in current multicore-based systems, and is hence described in more detail. Most of the examples and case studies in later chapters were conducted on Sandy Bridge systems.

Chapter 3 gives the details of white-box performance modeling. After a discussion of useful performance metrics and high-level scalability laws, the roofline model is discussed, together with a detailed account of its prerequisites and its potential for guided code optimizations. Multiple examples are given, including sparse matrix-vector multiplication. Using the failure of the roofline model in certain situation as a starting point, the ECM model is then developed and validated using a streaming benchmark. Complex application scenarios are left for Part II.

Chapter 4 develops the multicore power model based on three simple benchmarks that are prototypical for large classes of applications. Using the model, guidelines for energy-efficient computation with respect to single-core performance, clock speed, and the number of active cores are derived and validated using the benchmarks. Finally, the power model is used to define a design space for energy-efficient systems.

In Chapter 5 the structured performance engineering process is formulated, first in a coarse form without the explicit use of patterns. It is applied to an in-depth performance analysis and optimization study of a three-dimensional Jacobi smoother. Defining and categorizing performance patterns then paves the way for a refined view on performance engineering.

Chapter 6 uses performance engineering to develop an optimized implementation of a backprojection algorithm for volume reconstruction in medical imaging. Starting from a simple roofline model, which wrongly predicts a memory-bound situation, simple algorithmic and code optimizations are applied before using the ECM model to arrive at a better description of the performance of the code.

In Chapter 7 an implementation of the lattice-Boltzmann algorithm with two-relaxation-time collision operator and a sparse lattice representation is analyzed in view of SIMD vectorization, propagation pattern, and clock speed. The ECM and multicore power models are combined to yield a prediction for a possible performance-energy optimization space, in which an optimal operating point can be found. In the multi-node parallel case at strong scaling the influence of MPI communication overhead on these chip-level results is studied and the optimization space re-evaluated.

Finally, Chapter 8 gives a summary and an outlook to possible future work.

### Chapter 2

### **Computer architecture**

This chapter gives a brief overview of computer architecture, as far as it is relevant for the performance modeling and engineering approaches described later. Since this work is mostly about node-level issues, the focus is on the chip and node architecture. More detail can be found in [21].

A vast literature, including long-standing standard works [22], exists about this topic, but is mostly concerned with details that are for the most part irrelevant for the computational scientist. It is one of the important prerequisites for a good understanding of performance issues that architectural details should be exposed only as far as they are relevant for the modeling approach at hand.

### 2.1 Cores

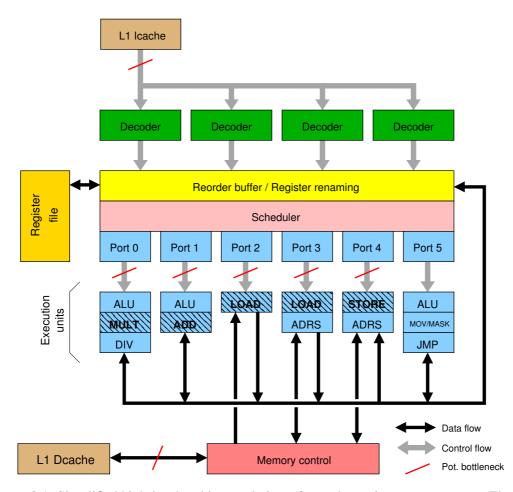

Figure 2.1 shows a simplified, high-level architectural view of a microprocessor core. It is somewhat similar to current Intel designs, but sufficiently general to cover the features of all modern microprocessors. The components will be described briefly in the following.

### 2.1.1 Execution units and ports

The execution units perform the actual work of the core in terms of carrying out the instructions in the machine code. Usually there are units for carrying out floating-point multiply and add operations (MULT/ADD), loading and storing data from and to the memory hierarchy (LOAD or STORE), for integer operations (ALU), for address generation (ADRS), for branching (JMP), for moving, masking, and shuffling data (MOV/MASK), and for special operations such as divide and square roots (DIV). Some of these functions share a unit; for instance, in the proto-typical design shown in Fig. 2.1 the floating-point MULT unit is shared with the DIV unit.

These units are usually pipelined, which means that a complex operation such as a floatingpoint MULT is split into several small steps, which can be executed in a single cycle (this would not be possible for the full operation). Pipelining makes it possible to run the core at higher clock frequencies, at the price of execution *latencies*: The latency is the number of clock cycles it takes after an operation was started until the result is available. For instance, a double-precision floating-point multiply has a latency (or *pipeline depth*) of five cycles on current Intel processors. Nevertheless, the pipeline can deliver one result per cycle if enough independent work is available and can be fed to it. In this case, the pipeline is *filled* and operates at its maximum throughput. Dependencies between operations cause pipeline *bubbles*, i.e., the maximum throughput cannot be met because one pipeline stage has to wait for another (possible in a different pipeline) to complete.

The cost for starting and stopping the pipeline counts as overhead, but is negligible if the number of independent operations is large compared to the pipeline depth. Not all operations are effectively pipelined. For example, divide and square root tend to be very expensive because their throughput is similar to their latency. On the other hand, multiple pipelines can potentially operate in parallel, leading to a maximum execution rate of more than one instruction per cycle. This is called *superscalarity* or *instruction-level parallelism* (ILP).

The execution units are fed via execution ports (which may be implemented as queues). In modern out-of-order designs the operations can be executed in any order that is compatible with the dependencies in the program flow, but the completion of the instructions is always in program order. Simpler architectures such as the Intel Xeon Phi coprocessor (in its current design) have in-order execution, which means that the order of instructions in the machine code is crucial, and software pipelining techniques mus be employed by the compiler or the

Figure 2.1: Simplified high-level architectural view of a modern microprocessor core. The most important execution units and potential bottlenecks are highlighted.

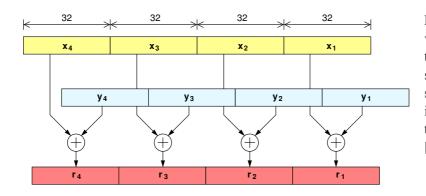

Figure 2.2: A SIMDvectorized ADD instruction, operating on four single-precision operands simultaneously. The register width is 128 bits in this case. (Figure from [21])

programmer.

### 2.1.2 Registers

All instructions that are executed by the core work with operands stored in processor *registers*. The access to data in a register is latency-free, but the number of registers is limited (e.g., current x86 processors have 16 floating-point and 16 general-purpose [integer] registers). The register file is usually larger than what is visible to the programmer, since the hardware employs register renaming techniques to work around simple dependencies in the machine code.

It is one of the complex tasks in compilers to figure out which variables should be kept in registers, and when they can be written out to the memory hierarchy. Usually one can make valid assumptions, such as that an accumulation variable in a loop is kept in a register at least until the loop is finished. These assumptions go into the peak performance estimates required for performance modeling (see Chapter 3).

### 2.1.3 SIMD execution

Single instruction multiple data (SIMD) allows for simultaneous execution of operations on multiple operands by a single machine instruction. To this end, the architecture provides registers which are wider than they would have to be to store only a single operand. In modern SIMD-equipped processors the SIMD width is between 128 bits and 512 bits, allowing for two to eight "tracks" in double precision (four to 16 in single precision). Figure 2.2 shows the example of an ADD instruction operating on two 128-bit registers and performing four single-precision floating-point additions at the same time. The term *vectorization* is frequently used when SIMD is employed. It is decisive for performance that the SIMD principle cannot only be applied to arithmetic operations but also to data transfers, since the data throughput to and from the L1 cache may be a bottleneck. In such a case, SIMD instructions should be used for both arithmetic and LOAD/STORE. If this is not possible because the operands are not consecutive in memory, SIMD has limited benefit. See Chapter 6.4.1 for an example.

If SIMD instructions cannot be used, one must revert to *scalar* instructions, which typically use only the lowest part of a register. More advanced SIMD instruction sets allow for arbitrary masking of operations, so that any combination of SIMD tracks can be blocked out. SIMD is also no restricted to floating-point computation. For instance, the 128-bit SSE ("Streaming SIMD Extensions") instruction set on modern x86 designs also contains integer operations.

Ideally, a SIMD width of k elements increases the arithmetic peak performance of the core

Figure 2.3: Simultaneous multi-threading allows the simultaneous execution of several (two in this case) threads on the same core. The threads share all resources except the register set. One thread can fill the bubbles left in the pipeline(s) by the other. (Figure from [21])

by a factor of k. Note that the SIMD concept is "orthogonal" to pipelining: There may be pipelining issues even if a code is perfectly SIMD-vectorized, since each SIMD track is a pipeline of its own in lockstep with the others, working on the same instruction(s) but on different data items.

#### 2.1.4 Instruction cache and decoders

Instructions are read in program order from the Level 1 instruction cache, whose maximum transfer rate is limited (although this is a bottleneck that does not very often apply in scientific computing). All instructions must be decoded before they can be executed. A limited number of decoders is available for this task. Intel and AMD x86 designs have the special feature that the machine code read from the instruction cache is not the code that runs in the execution units. X86 machine instructions are translated by the hardware into so-called micro-ops ( $\mu$ ops), which correspond to RISC-like instructions. RISC (Reduced Instruction Set Computing) is a design principle which allows only very simple instructions, so that they can be efficiently pipelined and executed at high clock frequencies. The x86 machine instruction set does not adhere to this principle, since it contains numerous complex instructions like the combination of a LOAD and an ADD. Splitting them to  $\mu$ ops on the fly allows for more efficient execution in the core. Most restrictions on instruction throughput apply to the  $\mu$ ops.

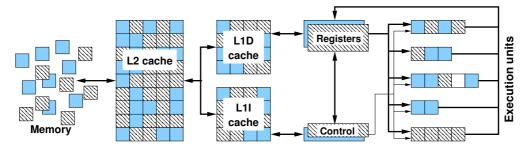

### 2.1.5 SMT

Simultaneous multi-threading (SMT) is used to increase the throughput of instructions on the core in certain cases. With SMT, a single core is able to execute multiple independent instruction streams at a time. To the applications and especially to the operating system it thus appears as multiple cores. However, almost all the resources are shared between the threads. The only fully duplicated resource is the register set, since each running program requires a full set of registers. It is certainly possible to run multiple processes or threads on a single core without SMT by time-sharing, but this is a feature of the operating system and not of the hardware.

The purpose of SMT is to make better use of the pipelines, which are often not fully utilized even with well-optimized software. Bubbles left in the pipeline stages by one thread or process can be filled by another (see Fig. 2.3). This can boost the throughput per core considerably in some cases (see Sect. 6 for an example). If the running threads are limited by a common

bottleneck outside the core pipelines, such as memory bandwidth or a shared queue, no benefit is expected.

For the application programmer, SMT is first and foremost a *topology* issue, because they must decide to use or to ignore the feature by proper binding of threads and processes to the resources.

### 2.1.6 Data cache

The results generated by executed instructions are either used from registers or eventually stored to the memory hierarchy. In general, the Level 1 data cache is the target for all LOAD and STORE operations. If a memory address is accessed whose contents are not already in the L1 cache (this event is called a *miss*), the corresponding cache line is read (the cache line size on x86 processors is 64 bytes). This pertains to STOREs as well: The cache line transfer initiated by a store miss is called a *write-allocate*.

### 2.1.7 Clock frequency and turbo mode

All operations in the execution core and the immediately connected caches run at the same clock speed (outer-level caches may run at a different frequency). This means that all performance numbers scale linearly with the clock frequency if no resources outside this area are used by the running code. Performance on this level is hence often discussed in terms of "amount of work per clock cycle," since this is a frequency-independent metric.

Modern processors often allow setting the clock frequency from user space. On Sandy Bridge and earlier designs this setting is global across all cores. Upcoming Intel processors will allow core-specific clock speeds.

A special feature found on all current x86 designs is "turbo mode" ("turbo core" for AMD). In turbo mode the chip can run faster than its nominal clock frequency, depending on the number of active cores and the die temperature. Intel processors even allow for a violation of the thermal design power (TDP) limit for a short amount of time. In view of Amdahl's Law, these measures are a way not only to increase the performance of sequential code but also to improve the scalability of parallel programs with non-negligible serial fraction.

### 2.2 Multicore chips

### 2.2.1 Multiple cores

To work around the power dissipation problems at high clock frequencies, processor manufacturers implement multiple cores on a die. This allows to make use of Moore's Law, i.e., the exponentially increasing transistor count per chip, within a constant power envelope.

Standard multicore processors feature a number of cache levels (usually two to three), most of which are private to each core. All caches except the L1 cache are traditionally unified, i.e., they can store instructions and data at the same time. The outer-level cache (OLC) is usually shared to allow for fast communication and synchronization between cores. When a cache line is brought from memory into the cache hierarchy there are essentially two options: In an *inclusive* cache hierarchy, any outer cache holds copies of all cache lines in the inner caches. An *exclusive* cache hierarchy always transfers cache lines to an inner level, from where they must be copied

Figure 2.4: Simplified high-level structure, or "topology," of a sharedmemory compute node based on two eight-core processors with Simultaneous Multi-Threading (SMT). I/O resources such as disks, network interfaces, or accelerator hardware, are connected via special buses, e.g., PCI Express.

down when replaced (evicted). A mixture of both concepts is also possible. Knowledge about the details of data transfers between the caches is required for accurate performance modeling (see Chapter 3 for examples).

Whenever multiple cores operate on different caches, a *cache coherence protocol* ensures that changes to different parts of the same cache line leave the caches in a consistent state. This can lead to performance problems if such changes happen in rapid succession, since cache lines have to be moved back and forth through the system ("false sharing").

#### 2.2.2 Memory access

The memory interface is usually shared among the cores on a chip, so it is a typical candidate for a bottleneck. Memory *latency* is the time it takes to set up a cache line transfer, and is typically of the order of hundreds of core cycles. The overall time to transfer a cache line is absolutely dominated by latency. Prefetching mechanisms, either in hardware or in software, help with hiding the memory latency and actually reach the *bandwidth* limit of the memory interface if the data access pattern is appropriate. Best results are achieved with regular, unit-stride ("streaming") memory access. If the access pattern is strided or erratic, the memory bandwidth may not be exhausted and excess data transfers will occur due to the cache line concept (a full cache line is transferred but only part of it may be used before it gets evicted). See Sect. 3.3.2 for an example on the consequences of erratic memory access.

The latency and bandwidth considerations for main memory also apply to the higher levels of the cache hierarchy. Even though the latencies are shorter and the bandwidths are higher than for memory, non-unit strides or erratic accesses lead to large penalties, too.

### 2.3 Node and memory architecture

Two-socket servers have been at the price-performance "sweet spot" in commodity-based high performance computing for the last ten years. Figure 2.4 shows the structure of a typical compute node. Usually there is one chip per socket, with its own memory interface (some current

AMD-based server processors are a notable exception with two chips per socket). The chips are coupled via an interconnect network, which makes the whole setup a shared-memory system. In the commodity sector this interconnect is either *QuickPath* (QPI) or *HyperTransport* (HT). All the installed memory, no matter to which socket it is attached, can be accessed transparently by any core, and cache coherence is automatic. This principle is called *ccNUMA* (cache coherent non-uniform memory access).

A ccNUMA system is divided into *locality domains*. If a core accesses memory in a distant domain, this is more expensive (in terms of latency and bandwidth) than in the local domain where the thread is running. The penalty for non-local access is typically larger in systems with many domains, and is significant in any case. In order to make sure that any memory access is as local as possible, programs should make use of the first-touch principle, or "Golden Rule of ccNUMA:" The mapping of physical to logical memory addresses takes place not at the allocation, but at the *initialization* of a memory page. A page gets mapped into the locality domain of the core that writes to it first. Two crucial consequences arise from this: First, memory should be initialized by the same thread that uses it in a parallel computation, and second, threads should be bound to cores so that they cannot be migrated by the operating system to another ccNUMA domain, thereby losing their locality of memory access.

As Fig. 2.4 shows, even a single current multicore, multi-socket system has a rich "topology." Topology is the structure of a system in terms of the location of cores (and SMT threads) and the resources that they share. SMT threads always share a core, cores on a chip share some cache levels and the memory interface, and sockets share the coherent network and typical I/O resources such as the network interface, disks, accelerators, etc. Since shared resources are prone to become bottlenecks, topology is an essential component in performance assessment and modeling. Knowing about the sensitivity of a parallel program to the typical hardware bottlenecks leads the way to well-founded code optimization efforts. Chapter 5 describes a workflow which is based on this idea.

### 2.4 Test bed and tools

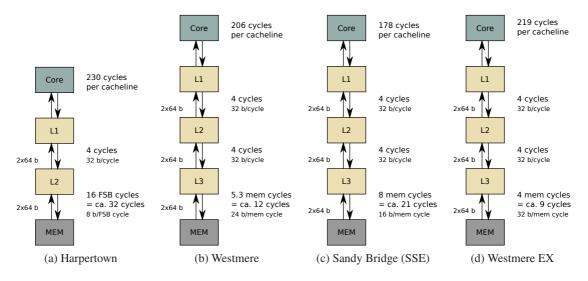

### 2.4.1 Intel Xeon "Sandy Bridge" processor [1]

Most of the performance data in this work was measured on compute nodes and systems based on the dual-socket eight-core Intel Sandy Bridge EP platform (Xeon E5-26XX). The Intel Sandy Bridge microarchitecture contains numerous enhancements in comparison to its predecessors, e.g., the "Westmere" and "Nehalem" chips. The following features are most important for the analysis in the following chapters [23]:

• Compared to SSE, the Advanced Vector Extensions (AVX) instruction set extension doubles the SIMD register width from 128 to 256 bits. At the same time, the load throughput of the L1 cache is doubled from 16 bytes to 32 bytes per cycle, so that a Sandy Bridge core can sustain one full-width AVX load and one half-width AVX store per cycle. With SSE or scalar execution, these limits are changed: In both cases the core can sustain either one load and one store, or two loads per cycle, to the effect that many loops do not show a 4× speedup of core execution when going from scalar mode to AVX (see Sect. 3.3.1 for an example).

- The core can execute one ADD and one MULT instruction per cycle (pipelined). With double-precision AVX instructions, this leads to a peak performance of eight flops per cycle (sixteen at single precision). In general, the core has a maximum instruction throughput of six  $\mu$ ops per cycle.

- Each core can execute two concurrent streams of instructions using simultaneous multi-threading (SMT).

- The L2 cache sustains refills and evicts to and from L1 at 256 bits per cycle (half-duplex). A full 64-byte cache line refill or evict thus takes two cycles. This is the same as on earlier Intel designs.

- The L3 cache is segmented, with one segment per core. All segments are connected by a ring bus. Each segment has the same bandwidth capabilities as the L2 cache, i.e., it can sustain 256 bits per cycle (half-duplex) for refills and evicts from L2. This means that the L3 cache is usually not a bandwidth bottleneck, which is an improvement compared to previous Intel processors.

- All parts of the chip, including the L3 cache (which is part of the "Uncore"), run at the same clock frequency, which can be set to a fixed value in the range from 1.2–2.7 GHz. The speed of the DRAM chips is constant and independent of the core clock.

- One Xeon E5-26XX socket has four DDR3-1333 or DDR3-1600 memory channels for a theoretical peak bandwidth of 42.7 GB/s or 51.2 GB/s. In practice, between 36 GB/s and 42 GB/s can be achieved with the standard STREAM benchmark [24] at high clock frequencies.

- Sandy Bridge is the first Intel processor exposing a power measurement infrastructure to the user code. Power and energy measurements reported in this work are for the "package" only, i.e., they ignore the installed RAM. Preliminary results for the power dissipation of installed DIMMs are between 2 and 9 W per socket (16 GB RAM in 4 DIMMs of 4 GB each), depending on the workload (memory-bound vs. cache-bound).

Some of these low-level hardware properties will be revisited when discussing performance models and results.

### 2.4.2 Tools

Source code was compiled with the Intel compiler in version 12.1 or 13.1. The tools of the LIKWID tool suite [25, 26] were employed for binding threads of OpenMP programs to cores (likwid-pin), for hardware performance monitoring (likwid-perfctr), and for energy measurement (likwid-powermeter).

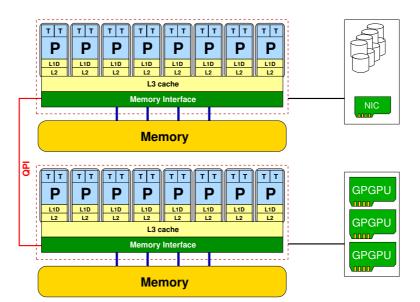

### 2.4.3 SuperMUC

The large-scale parallel runs of lattice-Boltzmann simulations used in Chapter 7 to demonstrate energy-efficient execution were conducted on the "SuperMUC" federal supercomputer at Leibniz Supercomputing Center  $(LRZ)^1$  in Garching near Munich. It is a tier-0 PRACE<sup>2</sup> system and

<sup>&</sup>lt;sup>1</sup>http://www.lrz.de/english/

<sup>&</sup>lt;sup>2</sup>http://www.prace-ri.eu/

one of the main federal compute resources in Germany. It is built from a number of 512-node "islands," with a fully non-blocking fat tree FDR10 InfiniBand connectivity inside each island. A compute node comprises two Intel Sandy Bridge EP (Xeon E5-2680) eight-core processors with a base clock frequency of 2.7 GHz.

The actual clock speed of the processors in SuperMUC can be influenced by a so-called "energy tag," which is supplied upon job submission together with a parameter specifying how much performance degradation the user wants to tolerate for their job. A heuristic based on hardware performance counter measurements of the user's previous jobs with the same energy tag then sets the clock frequency for the job (turbo mode cannot be used). These measures try to establish a user-friendly semi-automatic mechanism for saving energy.

### **Chapter 3**

# White-box performance modeling on the chip level

As described in Chapter 1, performance modeling can be a powerful tool for software engineering in computational science. Taking a modeling approach to the interaction of software with hardware is, while not new, a concept that is not yet in wide use. Since performance for problem solving is generated in the execution units of processor cores, and since all relevant computational resources are replicated when using multiple chips, modeling and optimization activities must start at the chip level. After revisiting high-level scalability models, this chapter introduces the well-known *roofline model* and the new *ECM performance model*. These models are shown to provide valuable insights into the performance properties of modern processor chips and the code that runs on them. In Chapter 5 the models will be put into the larger context of node-level performance engineering.

### **3.1** Performance and speedup

This section addresses performance and scalability of serial and parallel programs from an abstract point of view. In computing, *performance* is usually defined as *work* divided by *time*, where "work" is a problem (or a well-defined part thereof), and "time" is the wall-clock time required to solve it:

$$P = \frac{W}{T} \tag{3.1}$$

An accurate definition of "work" is crucial for a sensible assessment of performance. For instance, if solving the problem involves necessary overhead that takes time but is not in itself part of the result, this overhead does not constitute "work." Communication or synchronization in parallel computing are typical examples.

Parallel computing is often concerned with the question of how much more performance can be achieved if the work is done with "accelerated" resources, such as multiple cores, chips, or nodes, or with special hardware like GPGPUs. *Speedup* can thus be defined as

$$S = \frac{P_{\rm a}}{P_0} = \frac{W_{\rm a}}{W_0} \frac{T_0}{T_{\rm a}} , \qquad (3.2)$$

where  $P_a$  denotes "accelerated" performance and  $P_0$  is a given baseline level. This definition does not specify whether the same amount of work is done in the baseline and in the accelerated

case ( $W_0$  vs.  $W_a$ ). The baseline performance is frequently chosen to be equal to one, so that speedup and accelerated performance are identical. Another popular choice is  $W_0 = W_a$ , i.e., the same problem is solved in both cases.

### 3.1.1 Useful performance metrics

Most simulation tasks are centered around algorithms that require floating-point computations. A natural unit to choose for "work" is thus the floating-point operation, or *flop*. The peak "speed" of processors or whole systems is also usually given in flop/s, since it is the most generic and widely applicable measure for performance. It also allows for a rough first estimate of how "effectively" the compute resources of a system are utilized: A large deviation of actual from peak flop/s performance *might* indicate a problem with code execution that should be addressed. However, there are various objections to using flops for assessing program performance:

- The flop/s metric can be easily manipulated. It is straightforward to rewrite implementations so that the flop count is strongly increased, without improving the time to solution of the actual problem.

- Different implementations of one algorithm, or even machine codes generated by different compilers from the same source, can exhibit strongly deviating flop counts.

- There are algorithms which do not exclusively rely on floating-point computations.

Hence, one should be careful whenever the flops metric is used. Alternatives exist in many cases, such as in iterative solvers where one "iteration," or "update," may serve as a convenient and implementation-independent unit of work.

#### 3.1.2 High-level scalability models

It is clear that the concepts of *performance* and *speedup* must be clearly separated. Especially looking at speedup figures alone may lead to false conclusions about the "quality" of parallel or accelerated execution. In the end, all that counts is how much work per unit of time can be done; if  $P_0$  in (3.2) is small, the achievable speedup *S* may be significant even if  $P_a$  is mediocre. If and how it can be determined whether  $P_0$  or  $P_a$  are "good" will be the topic of Chapter 3.

Nevertheless, the speedup metric can still be useful, since it allows a quantitative judgment about how efficiently resources are put to use when not all of a program's execution can be accelerated. In many cases the speedup can be written as

$$S = \frac{W_{\rm a}}{W_0} \frac{T_{\rm s} + T_{\rm p}}{T_{\rm s} + T_{\rm p}^{\rm acc} + c} , \qquad (3.3)$$

where  $T_0 = T_s + T_p$  is the non-accelerated runtime of the program, and  $T_p$  is a part which can be perfectly accelerated so that this part takes a time of  $T_p^{acc}$  in the accelerated case. Note that  $T_p^{acc}$  may also include any change in runtime caused by  $W_0 \neq W_a$ , e.g., if the accelerated execution is performed on a bigger problem. The parameter *c* quantifies any overhead that is caused by the process of acceleration, such as communication or synchronization. Frequently the non-accelerated runtime  $T_0$  is normalized to one, so that  $T_s = s$  and  $T_p = p$  become "nonaccelerated" and "accelerated" fractions, respectively, and s + p = 1. At the same time one can set  $W_0 = s + p = 1$ . If we finally interpret a non-accelerated fraction as a part of the overhead, (3.3) becomes

$$S = \frac{W_{\rm a}}{p_{\rm acc} + \delta} , \qquad (3.4)$$

with  $\delta = c + s$ . The quantity  $p_{acc}$  is "accelerated, normalized runtime" and describes the "perfect" part of execution, while  $\delta$  contains all factors impeding good scalability.

Some important special cases are worth noting. If  $W_0 = W_a = 1$  and  $\delta = s$  we have  $p_{acc} = p/\alpha$ , where  $\alpha$  is an acceleration factor. This leads directly to *Amdahl's Law* [27],

$$S = \frac{1}{s + \frac{1-s}{\alpha}} \,. \tag{3.5}$$

It quantifies the *law of diminishing returns*: The more effort is put into improving one part of the problem (in this case the accelerated fraction p = 1 - s), the less effect it has on the overall time to solution. In the limit  $\alpha \to \infty$  we get  $S \to s^{-1}$ . If  $\alpha = N$ , with N being the number of "workers" used for solving the accelerated part, we speak of *strong scaling*, and "acceleration" becomes "parallelization." For finite c > 0 the effective speedup is diminished:

$$S = \frac{1}{s + \frac{1-s}{\alpha} + c} , \qquad (3.6)$$

and if  $c'(\alpha) > 0$  this means that the speedup does not even increase when the acceleration factor goes up. A typical example is OpenMP parallelization overhead, which is linear or logarithmic in the number of threads used for parallelizing a loop. If the amount of work in an OpenMPparallel loop is too small, performance will go down when the number of threads is increased.

If  $W_a = s + \alpha p$ , i.e., the accelerated problem size is increased by a factor which is equivalent to the achievable acceleration on p, (3.4) becomes

$$S = \frac{s + (1 - s)\alpha}{c} , \qquad (3.7)$$

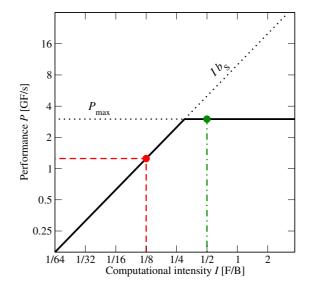

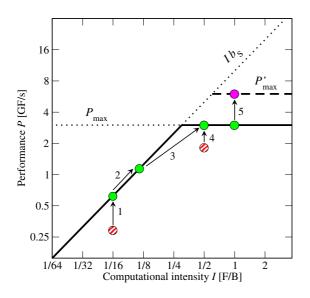

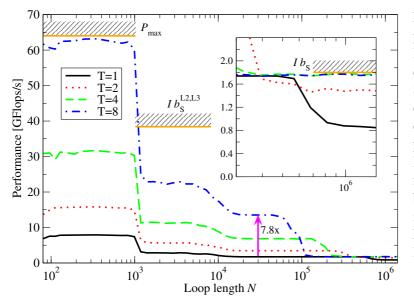

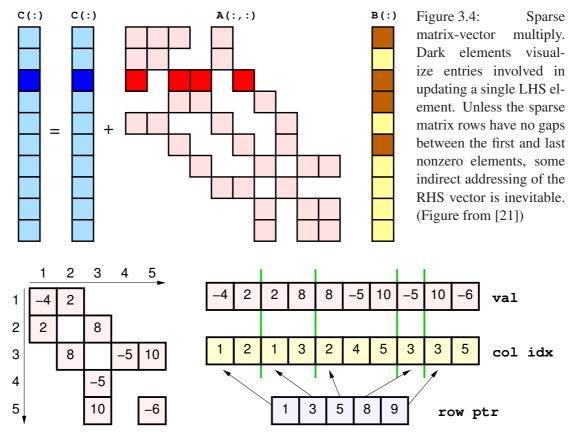

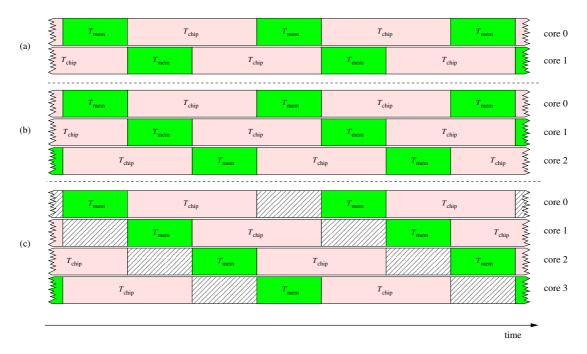

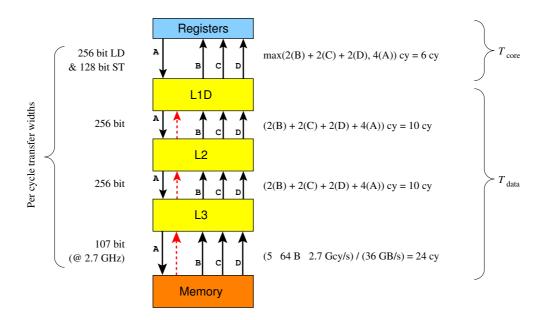

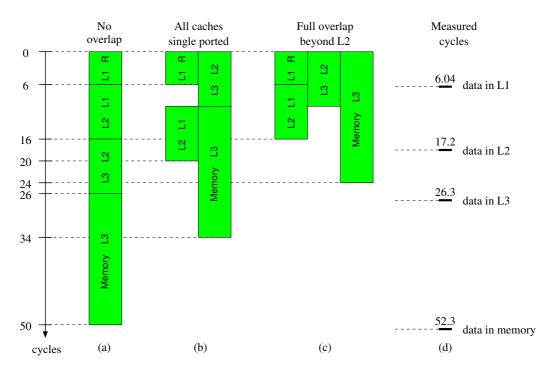

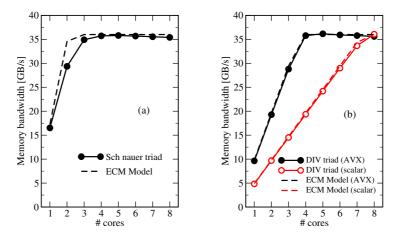

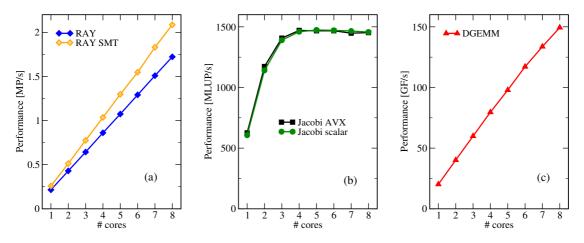

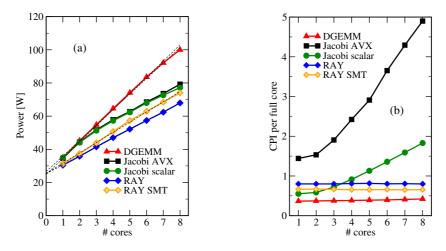

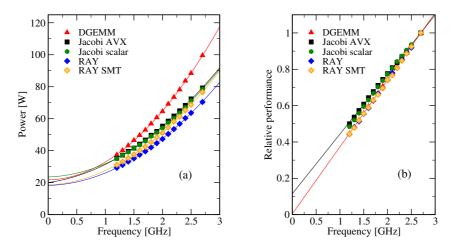

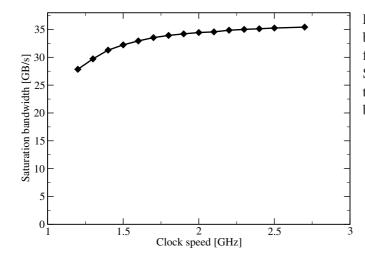

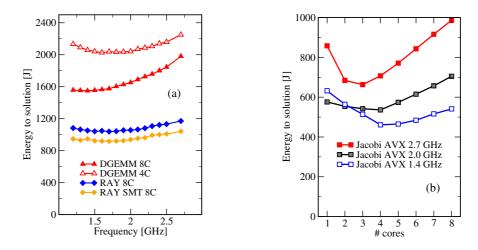

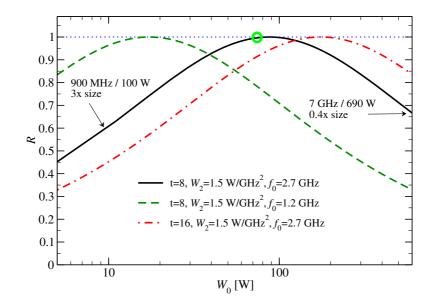

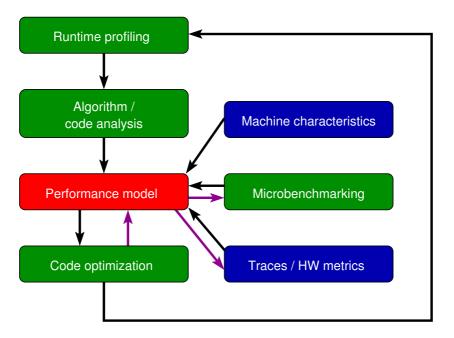

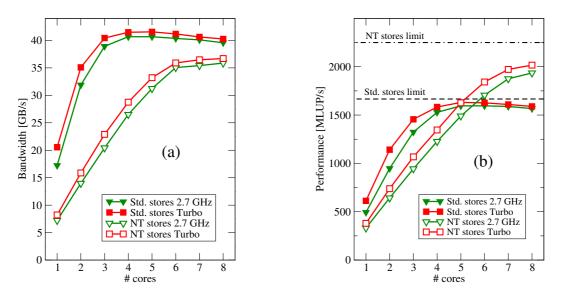

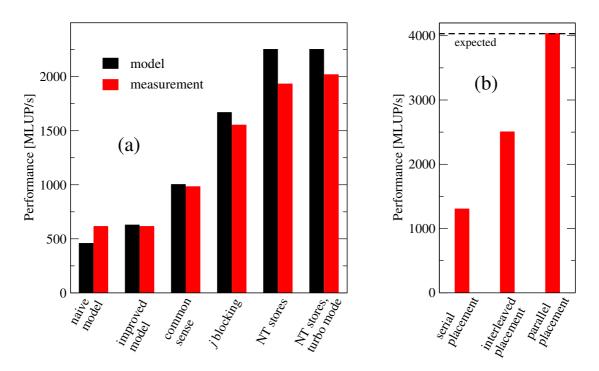

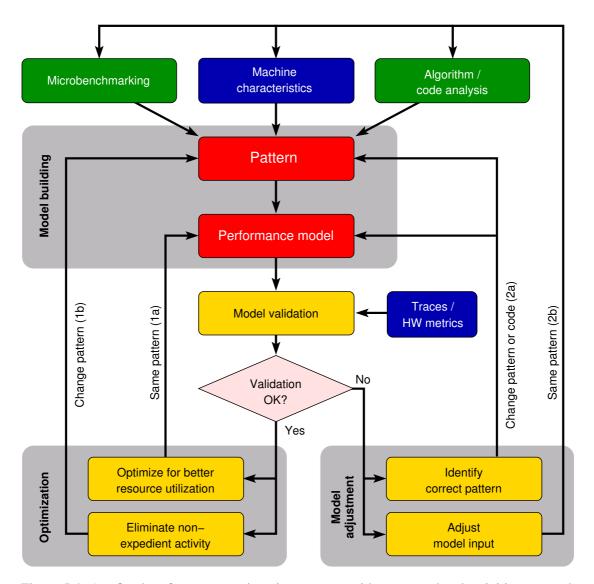

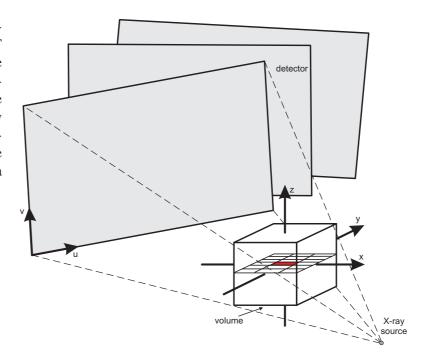

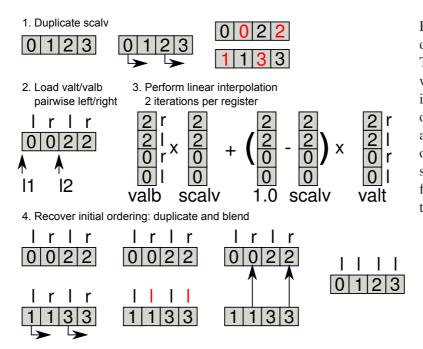

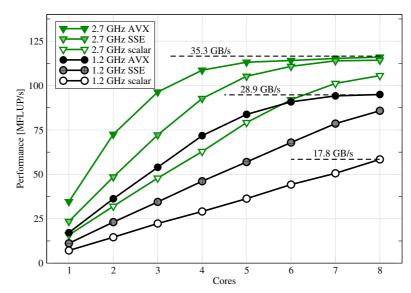

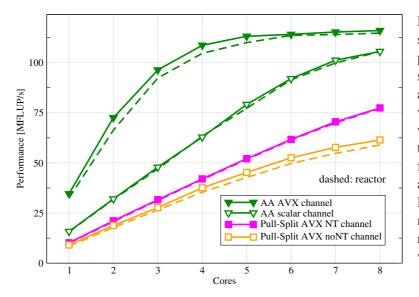

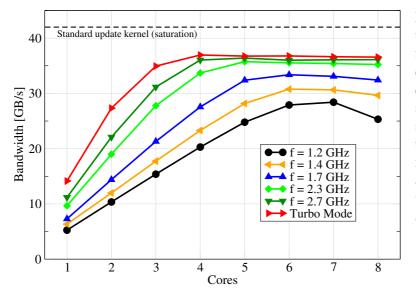

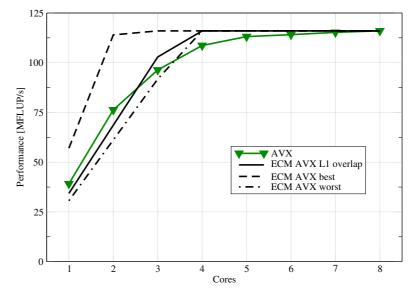

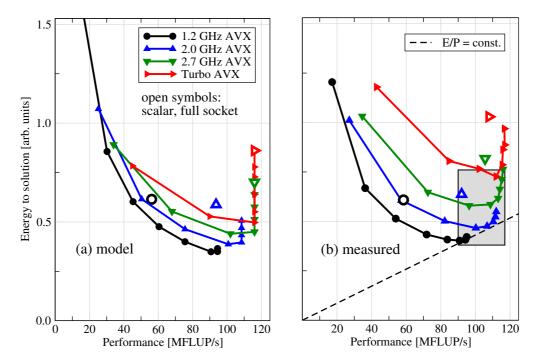

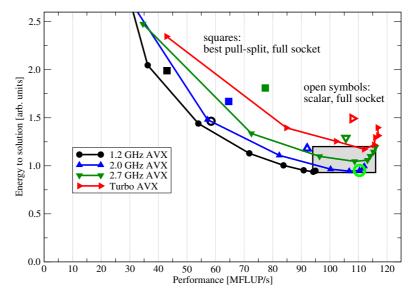

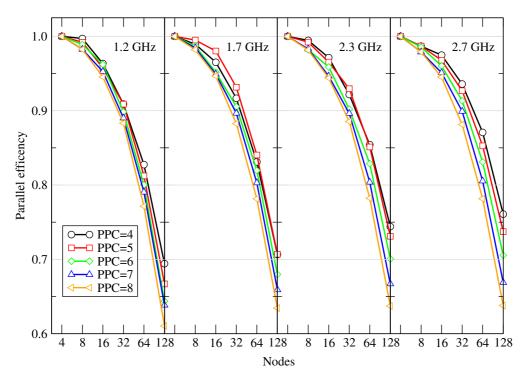

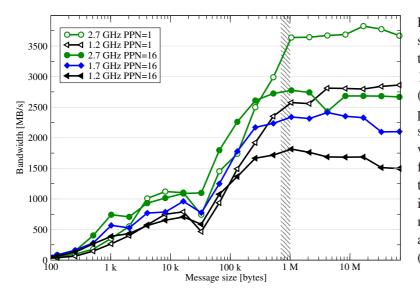

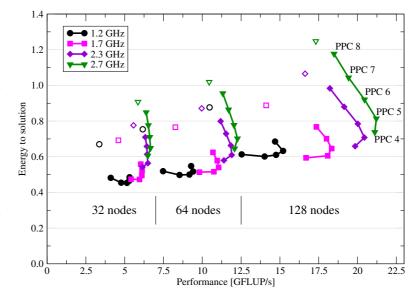

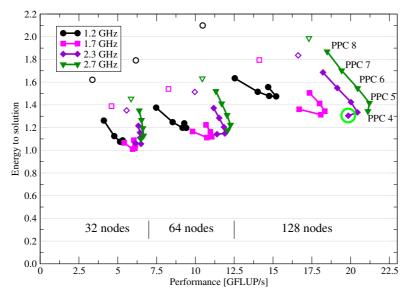

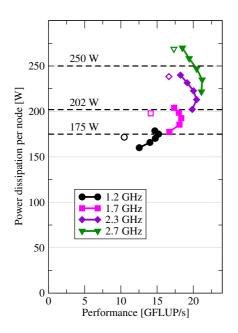

which is *Gustafson's Law*. For  $\alpha = N$  we speak of *weak scaling*. The impact of the overhead c on scalability is much weaker in this case. For large  $\alpha$  it is sufficient to have  $c'(\alpha) < 1$  for getting a speedup that grows without bounds.